БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

КАФЕДРА РЭС

РЕФЕРАТ

НА ТЕМУ:

«Триггеры с управлением записью вида  . Триггеры

J

-

K

-типа» . Триггеры

J

-

K

-типа»

МИНСК, 2009

Триггеры видов  относятся к разряду устройств, в которых прием и фиксация информации совмещены во времени. Это означает, что информация на выходах таких триггеров появляются практически одновременно с её поступлением на информационные входы для асинхронных и с поступлением тактирующего импульса (ТИ) на тактирующий вход С для синхронных триггеров. Термин «управление по уровню», как впрочем и любой другой способ управления записью, необходимо связывать с реакцией триггера на смену информации в процессе её записи. Применительно к тактируемым триггерам этот термин означает, что если, например, во время действия ТИ будет изменяться информация на логических входах, то это изменение будет непрерывно фиксироваться и на его выходах в течение всей длительность ТИ. относятся к разряду устройств, в которых прием и фиксация информации совмещены во времени. Это означает, что информация на выходах таких триггеров появляются практически одновременно с её поступлением на информационные входы для асинхронных и с поступлением тактирующего импульса (ТИ) на тактирующий вход С для синхронных триггеров. Термин «управление по уровню», как впрочем и любой другой способ управления записью, необходимо связывать с реакцией триггера на смену информации в процессе её записи. Применительно к тактируемым триггерам этот термин означает, что если, например, во время действия ТИ будет изменяться информация на логических входах, то это изменение будет непрерывно фиксироваться и на его выходах в течение всей длительность ТИ.

Реагируют на смену информации и асинхронные триггеры, поскольку тактируемые триггеры при постоянном разрешающем уровне на входе С становятся асинхронными. Другими словами, триггеры вида L реагируют на смену информации в процессе её записи, что является спецификой их работы, и это обстоятельство следует учитывать при их применении.

Рассмотрение триггеров вида  важно по той причине, что они кроме того, что имеют достаточно большое самостоятельное применение, являются по существу основными (базовыми) ячейками всех триггерных устройств, выполняя в них функции собственно триггеров определенного функционального типа. Наиболее часто в качестве собственно триггера используются асинхронные триггеры важно по той причине, что они кроме того, что имеют достаточно большое самостоятельное применение, являются по существу основными (базовыми) ячейками всех триггерных устройств, выполняя в них функции собственно триггеров определенного функционального типа. Наиболее часто в качестве собственно триггера используются асинхронные триггеры  и и  типов. Однако в качестве собственно триггера применяются и другие триггеры. Важно только, чтобы эти триггеры удовлетворяли двум требованиям: обладали полной системой переходов и выполнялись с возможно меньшим числом элементов (вентилей). типов. Однако в качестве собственно триггера применяются и другие триггеры. Важно только, чтобы эти триггеры удовлетворяли двум требованиям: обладали полной системой переходов и выполнялись с возможно меньшим числом элементов (вентилей).

Второе требование вытекает из условия, что собственно триггеры являются составной частью любого триггерного устройства и поэтому с целью сокращения аппаратурных затрат они должны иметь минимальное число элементов. Обращаясь к обобщенной схеме триггера, можно сказать, что собственно триггер есть не что иное, как триггерное устройство, у которого отсутствует устройство управления. В дальнейшем такие триггеры будем называть элементарными или простыми.

Требование полноты переходов означает, что для двух устойчивых состояний (состояние  называются единичными, а называются единичными, а  - нулевым) триггер обязан иметь следующие переходы при воздействии входных сигналов: - нулевым) триггер обязан иметь следующие переходы при воздействии входных сигналов:  . В частности переходы . В частности переходы  и и  означают, что при воздействии входных сигналов триггер должен сохранять свое предыдущее состояние, т.е. означают, что при воздействии входных сигналов триггер должен сохранять свое предыдущее состояние, т.е.  . Требование реализации с минимальными затратами по числу вентилей указывает на то, что триггер должен представлять собой асинхронный автомат с возможно меньшим числом входов. К числу таких принадлежат автоматы с двумя входами. . Требование реализации с минимальными затратами по числу вентилей указывает на то, что триггер должен представлять собой асинхронный автомат с возможно меньшим числом входов. К числу таких принадлежат автоматы с двумя входами.

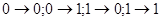

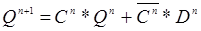

В общем случае для n сигналов, каждый из которых принимает два значения, существует  их возможных комбинаций. В результате, если n представляет собой число входов триггера, а его выходная функция принимает K дискретных значений, то формально можно построить их возможных комбинаций. В результате, если n представляет собой число входов триггера, а его выходная функция принимает K дискретных значений, то формально можно построить  триггеров различного логического типа. Учитывая, что выходная функция триггера может принимать пять значений, т.е. триггер может иметь пять логических состояний на выходе, а именно: триггеров различного логического типа. Учитывая, что выходная функция триггера может принимать пять значений, т.е. триггер может иметь пять логических состояний на выходе, а именно:

0 – триггер постоянно находится в нулевом состоянии независимо от изменения сигналов на его входе;

1 – триггер постоянно находится в единичном состоянии независимо от изменения сигналов на его входе;

состояние триггера не изменяется при изменении входных сигналов, причем может быть либо состояние триггера не изменяется при изменении входных сигналов, причем может быть либо  , либо , либо  ; ;

состояние триггера изменяется на противоположное при изменении входных сигналов, причем может быть изменение состояние 1 на состояние 0 или обратно; состояние триггера изменяется на противоположное при изменении входных сигналов, причем может быть изменение состояние 1 на состояние 0 или обратно;

Х – неопределенное состояние триггера, характеризующееся тем, что в процессе действия информационного сигнала на входе триггера, выходные логические уровни плеч триггера  и и  одинаковы ( одинаковы ( или или  ), а после окончания действия информационного сигнала триггер может перейти в состояние ), а после окончания действия информационного сигнала триггер может перейти в состояние  или или  с равной вероятностью, то число теоретически возможных типов триггеров с n информационными входами равно с равной вероятностью, то число теоретически возможных типов триггеров с n информационными входами равно  , где 5 – количество возможных состояний на выходе триггера, , где 5 – количество возможных состояний на выходе триггера,  - количество наборов содержащих все n входные переменные. Следовательно, при числе входов 2 (n=2) формально существует 625 типов триггеров (автоматов). Однако большинство из них либо не обладает полной системой переходов, либо тривиальны, либо просто бессмысленны. Примерами таких автоматов можно назвать автоматы, которые на всех наборах переменных принимают постоянные значения 0, 1, - количество наборов содержащих все n входные переменные. Следовательно, при числе входов 2 (n=2) формально существует 625 типов триггеров (автоматов). Однако большинство из них либо не обладает полной системой переходов, либо тривиальны, либо просто бессмысленны. Примерами таких автоматов можно назвать автоматы, которые на всех наборах переменных принимают постоянные значения 0, 1,  , ,  или неопределенное значение, или их комбинацию, например 0, Х, Q, X и т.д. Поэтому их 625 можно назвать сравнительно небольшое число триггеров (автоматов), которые могут обладать полной функцией переходов и иметь практический интерес. Технически реализуемых триггеров с одним информационным входом только 2, с двумя информационными входами – 24. Наиболее распространены двухвходовые триггеры, но синтезировано только восемь их типов, среди которых три – универсальные. Законы функционирования большинства из них приведены в таблице 1. или неопределенное значение, или их комбинацию, например 0, Х, Q, X и т.д. Поэтому их 625 можно назвать сравнительно небольшое число триггеров (автоматов), которые могут обладать полной функцией переходов и иметь практический интерес. Технически реализуемых триггеров с одним информационным входом только 2, с двумя информационными входами – 24. Наиболее распространены двухвходовые триггеры, но синтезировано только восемь их типов, среди которых три – универсальные. Законы функционирования большинства из них приведены в таблице 1.

Каждый из этих триггеров (автоматов) (табл. 1.) может быть исследован на предмет его принадлежности к элементарному триггеру. Однако элементарные триггеры необходимо выбирать среди автоматов, в которых отсутствуют состояния типа  , два , два  , поскольку реализация таких состояний требует наибольших затрат по числу элементов. Наибольший интерес для элементарных триггеров представляет автоматы 1, 2, 3 (табл. 1.) , поскольку реализация таких состояний требует наибольших затрат по числу элементов. Наибольший интерес для элементарных триггеров представляет автоматы 1, 2, 3 (табл. 1.)

Триггеры

RS

-типа

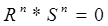

Автомат, поведение которого описывается переходами 1, носит название триггера RS-типа. Таким образом, триггером RS-типа называют элементарный автомат с двумя устойчивыми состояниями, имеющих два информационных входа R и S такие, что при R=1 и S=0 триггер принимает состояние 0 ( ), а при S=1 и R=0 – состояние 1 ( ), а при S=1 и R=0 – состояние 1 ( ). В соответствии с состоянием, принимаемым триггером, вход S называют единичным входом триггера, а вход R – нулевым. Закон функционирования RS-триггера в развернутом виде приведен табл. 2. ). В соответствии с состоянием, принимаемым триггером, вход S называют единичным входом триггера, а вход R – нулевым. Закон функционирования RS-триггера в развернутом виде приведен табл. 2.

Как следует из приведенных таблиц, состояние RS-триггера не изменяется (т.е.  ), если на обоих его входах действуют сигналы с уровнем 0. При одновременном поступлении на входы R и S сигналов с уровнем логической 1 триггер принимает неопределенное состояние (Х). Поэтому логические устройства на основе RS триггеров должны проектироваться с учетом исключения комбинации R=S=1. ), если на обоих его входах действуют сигналы с уровнем 0. При одновременном поступлении на входы R и S сигналов с уровнем логической 1 триггер принимает неопределенное состояние (Х). Поэтому логические устройства на основе RS триггеров должны проектироваться с учетом исключения комбинации R=S=1.

Таблица 2

Для нахождения характеристического уравнения RS-триггера запишем данные табл. 2. на карту Карно (рис. 4.).

Рис. 1 Карта Карно RS-тригера

Проводя этап считывания, находим

(1) (1)

Непосредственная реализация триггера RS-типа по уравнениям (1) в базисе ОФПН (основного функционально полного набора) приводит к триггеру вида  (рис.2.). (рис.2.).

Схема такого триггера имеет один выход, т.е. являются однофазной. На практике наиболее часто применяются RS-триггеры, обладающие как прямым, так и инверсным выходами, выполненные на элементах И-НЕ, ИЛИ-НЕ. Уравнения последних можно получить посредствам преобразования характеристического уравнения RS-триггера. Применив правило де Моргана (законы дуальности) к уравнению RS-триггера, получим

; (2) ; (2)

. (3) . (3)

Схемы RS-триггеров, построенные по уравнениям (2) и (3), их обозначения и диаграммы работы приведены на рис.3.

Из диаграммы видно, что смена информации на его входах в процессе записи (момент  ) отражается на его выходах ( ) отражается на его выходах ( ), что характеризует схему как триггер вида L. ), что характеризует схему как триггер вида L.

Кроме триггеров  -типа представляют интерес автоматы, поведение которых описывается функциями переходов 2 и 3 в табл. 1. Закон функционирования автомата 2 отражен в таблице 3.3 -типа представляют интерес автоматы, поведение которых описывается функциями переходов 2 и 3 в табл. 1. Закон функционирования автомата 2 отражен в таблице 3.3

Характеристическое уравнение такого триггера записывается следующим образом:

Составляя табл. 2. и 3., нетрудно заметить, что рассматриваемый автомат аналогичен триггеру RS-типа, но в отличие от него управляется инверсными сигналами. Поэтому такой автомат часто называют триггером RS-типа с инверсным управлением (инверсный RS-триггер) и обозначают как триггер вида  . .

| Рис.3. Схемы парафазного (R-S)L

-триггера на логических элементах ИЛИ-НЕ (а); И-НЕ (б); условное обозначение триггера (в) и диаграмма работы (г) |

|

Характеристическое уравнение триггера применительно к входам R и S имеет вид:

; ;  (4) (4)

Из табл. 3. и уравнений (4) следует, что для триггера вида  запрещенной является комбинация из двух логических нулей на входах, которые обозначаются буквами запрещенной является комбинация из двух логических нулей на входах, которые обозначаются буквами  и и  . .

Причем наличие черты указывает на тот факт, что триггер по информационным входам управляется сигналами с уровнем логического 0, т.е. в режиме хранения информации на входах  и и  действуют уровни логической 1. Однофазный вариант триггера, выполненного в базисе элементов ОФПН по уравнениям (4), и его условное обозначение приведены на рис.4. действуют уровни логической 1. Однофазный вариант триггера, выполненного в базисе элементов ОФПН по уравнениям (4), и его условное обозначение приведены на рис.4.

Рис.4. Схема однофазного (R-S)L

-триггера (а)

и его условное обозначение (б)

|

|

Парафазный вариант триггера, имеющего прямой и инверсные выходы, получатся либо путем инвертирования сигнала Q, либо посредствам преобразования уравнений (3.4) в базисе элементов И-НЕ:

(5) (5)

Триггер, построенный в соответствии с уравнением (5), и его условное обозначение показаны на рис.5.

| Рис.5. Схема парафазного (R-S)L

Tpnrrepa (a) и его условное обозначение (б). |

|

Триггеры

J

-

K

-типа

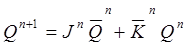

Триггером J-K типа называется устройство с двумя устойчивыми состояниями и двумя входами J и K, которое при условии J*K=1 осуществляет инверсию предыдущего состояния (т.е. при  ; ;  ), а в остальных случаях функционируют в соответствии с таблицей истинности R-S-триггера, при этом вход J эквивалентен входу S, а вход K – входу R. В табл. 1. этот триггер имеет номер 10. Закон функционирования J-K-триггера приведен в табл. 4. Как видно из табл. 4., триггер обладает полной системой переходов и вместе с тем у него отсутствуют запрещенные комбинации входных сигналов. ), а в остальных случаях функционируют в соответствии с таблицей истинности R-S-триггера, при этом вход J эквивалентен входу S, а вход K – входу R. В табл. 1. этот триггер имеет номер 10. Закон функционирования J-K-триггера приведен в табл. 4. Как видно из табл. 4., триггер обладает полной системой переходов и вместе с тем у него отсутствуют запрещенные комбинации входных сигналов.

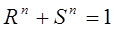

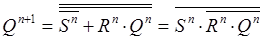

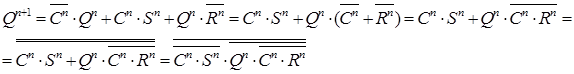

Занесем данные таблицы 4 на карту Карно:

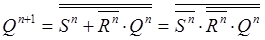

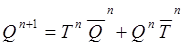

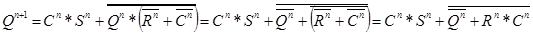

Из карты Карно, проведя этап считывания, находим характеристическое уравнение триггера:

(6) (6)

Построение триггера непосредственно по уравнению (6) приводит к схеме асинхронного JK-триггера, показанного на рис.6.

Если уровень 1 на входах J и K действует постоянно, то триггер будет находиться в колебательном режиме, поочередно переключаясь из 1 в 0 и из 0 в 1. Для устранения такого недостатка необходимо, чтобы комбинация сигналов J=K=1 оканчивалась сразу после переключения триггера в инверсное состояние. Последнее означает, что при комбинации сигналов J=K=1 триггер должен управляться не потенциальными, а импульсными сигналами, т.е. сигналами ограниченной и в данном случае жестко фиксированной длительностью.

| Рис. 6. Схема J-K триггера. |

|

Поскольку для выполнения такого требования в состав триггера необходимо дополнительно ввести схему управления, то схема триггера, приведенная на рис. 3.9. не является элементарной. Триггер J-K-типа относится к разряду универсальных триггеров, поскольку на его основе путем несложных внешних комбинационных изменений можно получить схемы выполняющие функции R-S,D- и T- триггеров. Способы применения триггера J-K-типа в качестве D-, T- и R-S-триггеров показаны на рис. 7.

| Рис. 7 Применение J-K-триггера в режиме D-(a), T-(б), R-S-(в) триггеров |

|

Из рис. 7. видно, что триггер J-K-типа будет функционировать в качестве D-триггера, если его вход J через инвертор подключить ко входу K. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Организация триггера со счетным входом показана на рис. 7, б. Счетный триггер на основе J-K-триггера получается при условии объединения входов J и K. R-S-триггер получается из триггера J-K-типа простым наложением ограничения на комбинацию входных сигналов J=K=1, т.е. эта комбинация сигналов не должна появляться на информационных входах триггера.

Триггеры J-K-типа находят применение при построении пересчетных схем, схем сдвиговых регистров, в устройствах управления и т.д.

Триггер

T

-типа

Триггер Т-типа (счетный триггер) называют логическое устройство с двумя устойчивыми состояниями и одним входом Т, изменяющее свое состояние на противоположное всякий раз, когда на вход Т поступает управляющий (счетный) сигнал. Закон функционирования триггера Т-типа приведен в таблице 5.

Этот триггер имеет один информационный вход Т. Из таблицы 3.5 видно, что при отсутствии информационного сигнала (Т=0) триггер Т-типа сохраняет свое исходное состояние 1 или 0, а при подаче информационного сигнала всегда переходит в инверсное состояние. Поскольку смена состояний триггера под действием входных сигналов эквивалентна счету, то такой триггер как бы осуществляет подсчет сигналов на 2, поэтому его часто называют счетным триггером или триггером со счетным входом. Иными словами, на выходе такого триггера, в ответ на два импульса на входе, появляется один импульс на выходе.

Характеристическое уравнение T-триггера имеет вид:

(7) (7)

Непосредственное построение триггера по уравнению (7) дает схемное решение Т-триггера (рис 8.)

| Рис. 8. Схема счетного триггера |

|

Сопоставляя схемы триггеров Т- и JK-типов (рис. 6. и рис. 8.) нетрудно заметить, что триггер Т-типа получается, как уже отмечалось (рис. 7, б), из триггера JK-типа посредствам объединения его информационных входов. Следовательно, этот триггер, как и триггер JK-типа на рис. 6. относится к разряду триггеров, управляемых импульсными сигналами, и поэтому не может являться элементарным.

Из этих двух примеров видно, что при наличии операции счета, которая в табл. 1. для различных комбинаций входных сигналов  и и  отражена символом отражена символом  , синтез триггеров по их характеристическим уравнениям приводит к асинхронным триггерам, которые не могут являться элементарными ввиду сложности выполнения требований по длительности входных сигналов. По этой причине отпадает надобность в исследовании на принадлежность к элементарным всех триггеров, имеющих в таблице истинности операцию счета (триггеры под номерами 9, 10, 12, 14, 16, 17 и т.д. табл. 3.1). Необходимо отметить, что рассмотренные элементарные триггеры реализуются с минимальными затратами по числу типовых элементов и именно они используются при синтезе более сложных триггерных устройств. , синтез триггеров по их характеристическим уравнениям приводит к асинхронным триггерам, которые не могут являться элементарными ввиду сложности выполнения требований по длительности входных сигналов. По этой причине отпадает надобность в исследовании на принадлежность к элементарным всех триггеров, имеющих в таблице истинности операцию счета (триггеры под номерами 9, 10, 12, 14, 16, 17 и т.д. табл. 3.1). Необходимо отметить, что рассмотренные элементарные триггеры реализуются с минимальными затратами по числу типовых элементов и именно они используются при синтезе более сложных триггерных устройств.

Тактируемые триггеры

Запись информации в тактируемые триггеры может осуществляться только при наличии ТИ. Следовательно, тактируемые триггеры кроме информационных обязаны иметь еще и тактирующий вход. В тактируемом исполнении может быть выполнен любой из триггеров таблицы 3.1.

Однако в практике проектирования тактируемых триггеров наибольшее распространение получили триггеры CRS- и CD- типов. Они являются по существу базовыми триггерами, на основе которых строятся более сложные схемы.

Триггеры

типа

типа

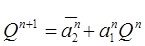

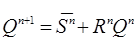

Поведение тактируемого триггера CRS-типа отражено в таблице 6.

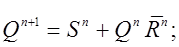

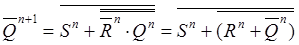

Характеристическое уравнение CRS-триггера имеет вид:

; ;  (8) (8)

Реализация триггера непосредственно по уравнению (8) в базисе ОФНП приводит к однофазному триггеру  типа. Однако в таком виде типа. Однако в таком виде  триггер не находит применения. Наиболее часто триггер не находит применения. Наиболее часто  триггеры выполняются в базисе элементов И-НЕ и И-ИЛИ-НЕ. триггеры выполняются в базисе элементов И-НЕ и И-ИЛИ-НЕ.

Схемы таких триггеров и их обозначение показаны на рис. 9.

Обе схемы можно получить посредствам преобразования уравнения (8).

| Рис. 9. Схема триггеров CL

RS-тиna на элементах И-НЕ (а), И-ИЛИ-НЕ (б), условное обозначение триггера (в) и диаграмма работы (г). |

|

В частности, схема триггера на рис. 9,а получается в результате следующих преобразований уравнения:

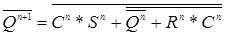

Для схемы второго триггера уравнение преобразуется следующим образом:

После инвертирования обеих частей уравнения получим необходимое выражение для реализации триггера (рис. 3.12, б) в базисе элементов И-ИЛИ-НЕ:

. .

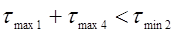

Обе схемы фиксируют информацию по уровню ТИ при условии, что τти

>3τср

и τти

>2τср

для схем на рис. 9, а и 9, б соответственно.

Из диаграммы на рис. 9, г видно, что смена информации на входах триггера при действии ТИ (моменты t1

-t3

) отражается на его выходах.

| Рис. 10. Схемы C-L

RS - триггера на элементах И-НЕ (а), И-ИЛИ-НЕ(б) и его условное обозначение (в) |

|

На рис. 10 приведены схемы триггеров  -типа. Триггеры управляются сигналами с уровнем логического 0, и для них запрещенной является комбинация двух 0 на его информационных входах при наличии ТИ с уровнем 0 (C=0). Обе схемы находят широкое применение; при этом схема на рис. 10, а выполняется на четырех элементах И-НЕ, а схема на рис. 10, б — на двух элементах И-ИЛИ-НЕ, то есть является более экономичной по числу вентилей, потребляемой мощности и более быстродействующей. -типа. Триггеры управляются сигналами с уровнем логического 0, и для них запрещенной является комбинация двух 0 на его информационных входах при наличии ТИ с уровнем 0 (C=0). Обе схемы находят широкое применение; при этом схема на рис. 10, а выполняется на четырех элементах И-НЕ, а схема на рис. 10, б — на двух элементах И-ИЛИ-НЕ, то есть является более экономичной по числу вентилей, потребляемой мощности и более быстродействующей.

Триггеры  -типа -типа

Триггером D-типа, известным под названием триггера задержки,

называют логическое устройство с двумя устойчивыми состояниями и одним информационным входом в (от англ. Delay — “задержка”). Закон функционирования триггера D-типа приведен в табл. 7 и аналитически описывается уравнением:

Таблица.7

То, что триггер имеет один информационный вход, в ряде случаев является достоинством триггеров D-типа по сравнению с триггерами с двумя информационными входами, поскольку в 2 раза сокращается число межкаскадных связей, требуемых для передачи информации. Именно в силу этого положительного свойства триггеры D-типа весьма широко применяются в интегральной схемотехнике при проектировании цифровых устройств.

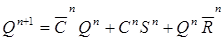

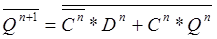

Построение триггера по характеристическому уравнению приводит к схеме, представляющей собой вентиль И с одним входом. Поскольку сигнал на выходе такой схемы отслеживается с некоторой задержкой, то триггер называют триггером задержки. В асинхронном исполнении D-триггер эквивалентен линии задержки, так как передает логический сигнал на выход с задержкой, определяемой задержкой самого логического элемента. Однако как триггер такая схема, естественно, существовать не может. В качестве триггера схема, описываемая табл. 7, существует только в тактируемом варианте. Но в этом случае она представляет собой один из 625 типов триггеров с двумя входами, а именно триггер под номером 7 в табл. 1. Поведение такого триггера в обобщенном виде описывается табл. 8 и характеристическим уравнением вида:

(9) (9)

Реализация триггера по уравнению (9) в базисе ОФПН дает однофазный триггер (рис. 11). В отсутствие тактирующего сигнала (С=0) триггер может находиться либо в состоянии 0 (Q=0), либо в состоянии 1 (Q=1). Пусть триггер находится в состоянии Q=1. В этом случае уровень 1 действует на выходе вентиля В1

и следовательно, на выходе элемента В3

, выполняющего функцию ИЛИ. Если триггер находится в состоянии 0 (Q=0), то закрыты оба вентиля В1

и В2

(на выходах уровни 0) и тем самым поддерживается уровень 0 на выходе Q триггера.

| Рис. 12. Схема однофазного CL

D триггера на одном элементе T-TTL-типа. |

|

| Рис. 11. Схема однофазного CL

D триггера на элементах И, ИЛИ, НЕ. |

|

Пусть триггер находится в состоянии Q=0. Установим его в состояние Q=1, для чего на входы подадим комбинацию сигналов C=1, D=1. В этом случае на выходе вентиля В2

, а затем и на выходе Q триггера формируется уровень 1. Последний поступит на вход вентиля В1

и подготовит его к включению по одному входу. В результате при C=0, то есть при съеме тактирующего сигнала, и при D=1 на выходе вентиля В1

сформируется уровень 1, который через элемент В3

подтвердит состояние Q=1 после съема ТИ. Однако такого подтверждения может не произойти, если после окончания ТИ вентиль В1

не успеет включиться, но уже выключится вентиль В2

, то есть на его выходе сформируется уровень 0 раньше, чем уровень 1 на выходе вентиля В1

. Другими словами мы сталкиваемся с явлением состязаний (гонок) между логическими элементами В4

, В1

и В2

.Говорят, что элемент В2

выиграет гонку, если сигнал на его выходе появится раньше, чем на выходе элемента В1

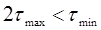

. Поэтому здесь необходима проверка триггера на функциональную надежность. Схема триггера рис. 11 при наличии состязаний будет считаться функционально надежной, если выполняется условие:

. .

. .

Рис. 13. Схема парафазного CL

D триггера (а-в) и диаграмма

их работы (г)

|

|

Это выражение можно записать в виде:

Полученное условие для однотипных элементов невыполнимо, так как для них всегда  . А это означает, что схема триггера будет функционально надежна, если в качестве вентиля В1

будет применяться элемент другой, по быстродействию серии ИМС, либо триггер реализуется на одном элементе T-TTL-типа (рис. 3.15). . А это означает, что схема триггера будет функционально надежна, если в качестве вентиля В1

будет применяться элемент другой, по быстродействию серии ИМС, либо триггер реализуется на одном элементе T-TTL-типа (рис. 3.15).

Различные схемные варианты триггеров D-типа приведены на рис. 13, а - в. Поскольку все триггеры вида L, то необходимо следить за тем, чтобы во время действия ТИ информация на входе оставалась постоянной (рис. 13, г). Анализируя схемы на рис. 13, а-в, нетрудно заметить, что все они выполняют одну и ту же логическую функцию, имеют одну и ту же диаграмму входных и выходных сигналов (рис. 13, г), но вместе с тем реализуется на различном числе элементов.

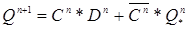

Приведенные схемы D-триггеров тактируются сигналами высокого уровня (C=1). Иногда требуются  -триггеры, функционирование которых описывается табл. 9 и характеристическим уравнением (3.10), составленным по карте Карно (рис. 14). -триггеры, функционирование которых описывается табл. 9 и характеристическим уравнением (3.10), составленным по карте Карно (рис. 14).

(10) (10)

| Рис. 14. Карта Карно CL

D триггера |

|

В схемотическом плане такие триггеры могут быть построены на основе триггеров рис. 14, а, б посредством замены элементов И-НЕ на элементы ИЛИ-НЕ. Однако наиболее экономичные по числу вентилей однофазный и парафазный варианты  -триггеров, приведенные на рис. 15. -триггеров, приведенные на рис. 15.

Однофазный вариант  -триггера (рис. 15, а) получается из уровнения (10), а парафазный — инвертированием правой и левой его частей, то есть из выражения: -триггера (рис. 15, а) получается из уровнения (10), а парафазный — инвертированием правой и левой его частей, то есть из выражения:

. .

Обе схемы функционально надежны и работают по низкому уровню ТИ (С=0). Кроме триггеров  - и - и  -типов широко применяются триггеры с числом информационных и тактирующих входов больше двух, а также триггеры с совмещенными режимами записи и фиксации информации. В качестве примера покажем триггер, схема которого изображена на рис. 16. -типов широко применяются триггеры с числом информационных и тактирующих входов больше двух, а также триггеры с совмещенными режимами записи и фиксации информации. В качестве примера покажем триггер, схема которого изображена на рис. 16.

| Рис. 16. Схема CL

S-RL

-триггера |

|

Триггер имеет два входа R и S (вход R асинхронный, вход S тактирующий). С этих позиций данный триггер следует назвать триггером  -типа. Иногда такой триггер называют двухтактным триггером D-типа. Это объясняется тем, что рассматриваемый и подобный ему триггеры работают, как правило, в режиме требующем двухтактной сетки синхро-частот ТИ1

=С1

и ТИ2

=С2

. При этом импульс С1

обнуляет триггер, а импульс С2

устанавливает его в единичное состояние при условии, что на входе S действует уровень логической 1. В результате при таком режиме работы для установки триггера в любое из двух состояний достаточно подать информационный сигнал только по одному входу аналогично триггерам D-типа. -типа. Иногда такой триггер называют двухтактным триггером D-типа. Это объясняется тем, что рассматриваемый и подобный ему триггеры работают, как правило, в режиме требующем двухтактной сетки синхро-частот ТИ1

=С1

и ТИ2

=С2

. При этом импульс С1

обнуляет триггер, а импульс С2

устанавливает его в единичное состояние при условии, что на входе S действует уровень логической 1. В результате при таком режиме работы для установки триггера в любое из двух состояний достаточно подать информационный сигнал только по одному входу аналогично триггерам D-типа.

ЛИТЕРАТУРА

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. М.: Мир, 2001. - 379 с.

2. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.: ИНТУИТ.РУ, 2003. - 440 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.: Политехника, 2006. - 885 с.

4. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш. шк., 2001. - 526 с.

5. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. М.: Радио и связь, 2000. - 416 с.

6. Соломатин Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. - 160 с.

|